## Technical Reference Manual

P/N: CHS-R3L-00-32

© 2003 ATI Technologies Inc.

#### **CONFIDENTIAL MATERIAL**

All information contained in this manual is confidential material of ATI Technologies Inc. Unauthorized use or disclosure of the information contained herein is prohibited.

You may be held responsible for any loss or damage suffered by ATI for your unauthorized disclosure hereof, in whole or in part. Please exercise the following precautions:

- Store all hard copies in a secure place when not in use.

- Save all electronic copies on password protected systems.

- Do not reproduce or distribute any portions of this manual in paper or electronic form (except as permitted by ATI).

- Do not post this manual on any LAN or WAN (except as permitted by ATI).

Your protection of the information contained herein may be subject to periodic audit by ATI. This manual is subject to possible recall by ATI.

The information contained in this manual has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

ATI, *mach64*, **3D** RAGE, RAGE THEATER, RAGE XL and RAGE 128 are trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

## **Record of Revisions**

| Release                           | Date                 |  |  |

|-----------------------------------|----------------------|--|--|

| 0.01-0.05<br>(previously 2.0-2.4) | Oct 1998 to Jan 1999 |  |  |

| 0.06                              | Mar 1999             |  |  |

| 0.07                              | Apr 1999             |  |  |

| 0.08                              | July 1999            |  |  |

| 1.00                              | Aug 1999             |  |  |

| 1.01                              | Nov 1999             |  |  |

| 2.00                              | Dec 1999             |  |  |

| 2.01                              | Mar 2000             |  |  |

| 2.02                              | May 2000             |  |  |

| 2.03                              | Oct 2000             |  |  |

| 3.00                              | Nov 2001             |  |  |

| 3.1                               | Sep 2003             |  |  |

| 3.2                               | Dec 2003             |  |  |

See Appendix B for revision history

## **Related Manuals**

## RAGE XL series

- RAGE<sup>TM</sup> XL Register Reference Guide (RRG-G04300)

- RAGE<sup>TM</sup> XL Design Guide (DRS-D04300)

## **Table of Contents**

| Chapt | er 1: Ii                                                                      | ntroduction                                                                                                                                                                                 |                                        |

|-------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.1   | About 7                                                                       | This Manual                                                                                                                                                                                 | 1-1                                    |

| 1.2   | ATI Co                                                                        | mponent Part Number Legend                                                                                                                                                                  | 1-2                                    |

| 1.3   | Conven<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4                                    | tions and Notations Pin/Signal Names Pin Types Numeric Representation Acronyms                                                                                                              | 1-3<br>1-3<br>1-4                      |

| Chapt | er 2: 0                                                                       | verview                                                                                                                                                                                     |                                        |

| 2.1   | Feature                                                                       | Summary                                                                                                                                                                                     | 2-1                                    |

| 2.2   | General                                                                       | l Features                                                                                                                                                                                  | 2-1                                    |

| 2.3   | RAGE 2<br>2.3.1<br>2.3.2<br>2.3.3                                             | XL Compatibility with other ATI Chips  Feature Compatibility with RAGE 128 VR  RAGE 128 Features Not Supported by RAGE XL  Feature Compatibility with the RAGE PRO                          | 2-2<br>2-3                             |

|       | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9 | s in Detail Integrated TMDS Digital Flat Panel Support. ACPI Power Management Floating-Point Set-up Engine Memory Support DVD and Video Support 2D Acceleration 3D Acceleration AMC Support | 2-5<br>2-6<br>2-6<br>2-6<br>2-7<br>2-7 |

|       |                                                                               | inout and Strap Descriptions                                                                                                                                                                | .2-10                                  |

| 3.1   | Pinout S                                                                      | Summary                                                                                                                                                                                     | 3-1                                    |

| 3.2   | RAGE XL Pin Assignment: Top View                                           | <i>3-2</i> |

|-------|----------------------------------------------------------------------------|------------|

| 3.3   | Host Bus Interface                                                         | 3-3        |

| 3.4   | Video Memory Interface                                                     | 3-5        |

| 3.5   | BIOS Memory Interface                                                      | 3-5        |

|       | 3.5.1 BIOS EPROM Memory Interface Mapping                                  |            |

| 3.6   | Multimedia Interface                                                       | 3-6        |

|       | 3.6.1 Multimedia Interface Pinout.                                         |            |

|       | 3.6.2 Standard Multimedia Configurations                                   | 3-7        |

| 3.7   | TMDS Interface for Digital Flat Panels                                     | 3-7        |

| 3.8   | CRT Monitor Interface                                                      | 3-9        |

|       | 3.8.1 CRT Monitor Interface                                                |            |

|       | 3.8.2 Panel Control Interface.                                             | 3-9        |

| 3.9   | Miscellaneous Pins                                                         | 3-10       |

|       | 3.9.1 Internal PLL and External Crystal Interface.                         |            |

|       | 3.9.2 Testing Pin                                                          |            |

|       | 3.9.3 Clamping Pins.                                                       |            |

|       | 3.9.4 Power and Ground Pins.                                               |            |

| 3.1   | 0 Strapping Options                                                        |            |

|       | 3.10.1 Standard Boot-up Sequence                                           |            |

|       | 3.10.2 Configurations for Strap/BIOS Implementation                        |            |

|       | 3.10.3 External Straps                                                     |            |

|       | 3.10.4 Bus Configuration Settings. 3.10.5 BIOS ROM Straps.                 |            |

|       | 3.10.6 Chip ID                                                             |            |

| 2.1   |                                                                            |            |

| 3.1   | <ul><li>1 Pinout Differences between RAGE XL and other ATI Chips</li></ul> |            |

|       | 3.11.2 Pinout Differences between RAGE XL and RAGE 128 VR                  |            |

|       | 3.11.3 Function Support Differences between RAGE XL and RAGE PRO           |            |

|       | 3.11.4 Power Differences between RAGE XL and RAGE PRO                      |            |

|       | 3.11.5 Similarity and Differences between RAGE XL and RAGE Mobility        | 3-22       |

|       |                                                                            |            |

| Chapi | ter 4: Functional and Interfacing Descriptions                             |            |

| 4.1   | 3D Graphics Coprocessor                                                    | 4-2        |

| 4.2   | 2D Engine                                                                  | 4-3        |

| 4.3   | IDCT Engine                                                                | 4-4        |

| 4.4   | Display System                                                             | 4-5        |

|       | 4.4.1 Extended VGA Graphics Controller                                     |            |

|    | 4.4.2           | CRT Controller (CRTC)                                      | 4-5  |

|----|-----------------|------------------------------------------------------------|------|

|    | 4.4.3           | Display Controller                                         |      |

|    | 4.4.4           | Hardware Cursor                                            |      |

|    | 4.4.5           | Video Coprocessor                                          |      |

|    | 4.4.6           | DVD Subpicture                                             |      |

|    | 4.4.7           | Palette and CRT DAC                                        |      |

|    | 4.4.8           | LCD Engine and Panel Interface                             |      |

|    | 4.4.9<br>4.4.10 | TMDS Interface Ratiometric Expansion                       |      |

|    |                 | ower Management.                                           |      |

|    | -               | •                                                          |      |

|    |                 | uple Clock Synthesizer                                     |      |

|    |                 | ultimedia Channel (AMC)                                    |      |

|    |                 | us Interface                                               |      |

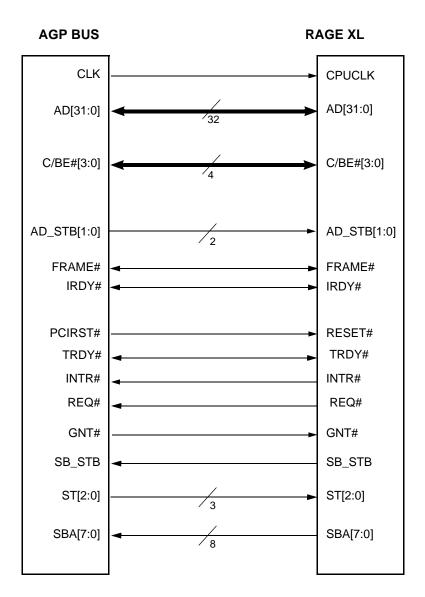

|    | 4.8.1           | AGP Bus Interface.                                         |      |

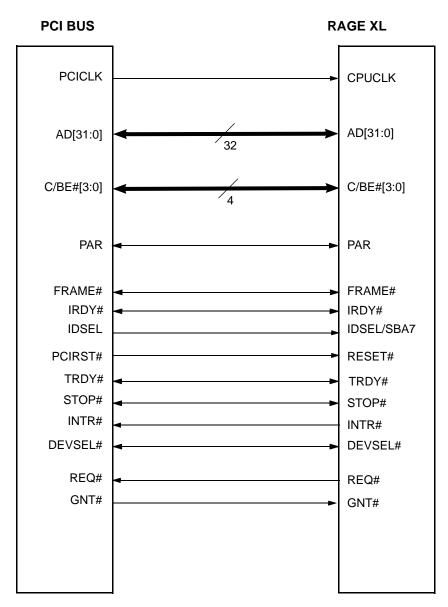

|    | 4.8.2           | PCI Bus Interface                                          | 4-12 |

|    | 4.9 Memor       | ry Controller and Interface                                | 4-13 |

|    | 4.9.1           | Memory Configurations.                                     | 4-13 |

|    | 4.9.2           | Memory Interface Mapping                                   |      |

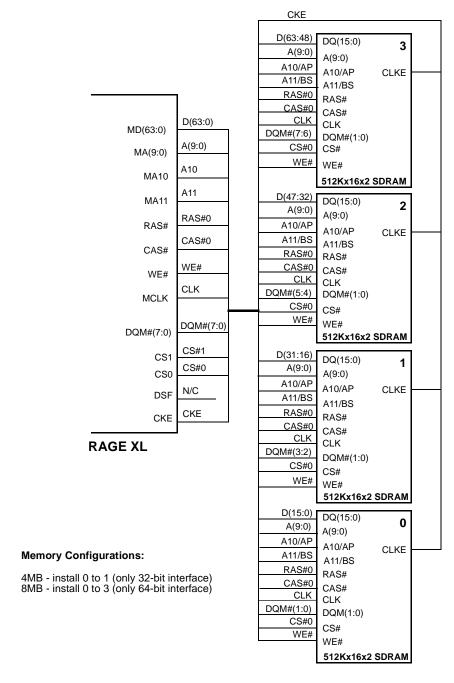

|    | 4.9.3           | SDRAM Interface with 512Kx16x2 (16 Mbit) Devices (RAGE XL) |      |

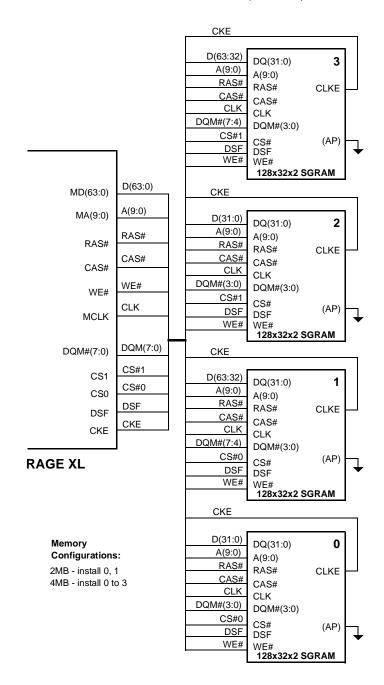

|    | 4.9.4           | SGRAM Interface with 128x32x2 (8 Mbit) Devices             |      |

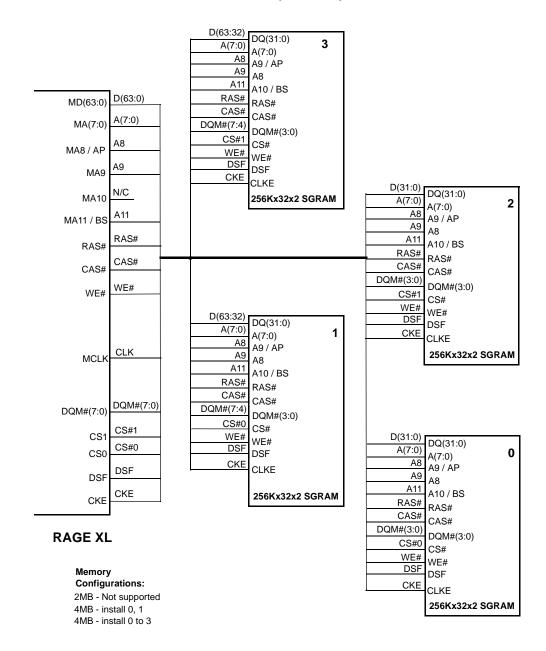

|    | 4.9.5           | SGRAM Interface with 256x32x2 (16 Mbit) Devices            |      |

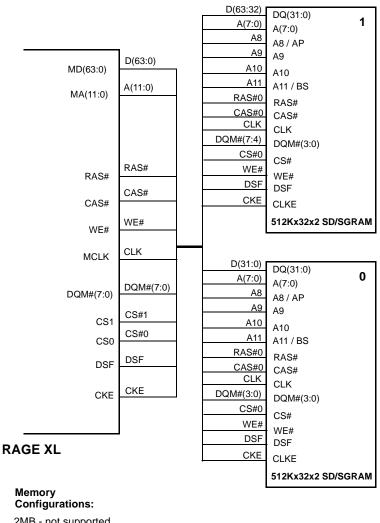

|    | 4.9.6           | SGRAM Interface with 512Kx32x2 (32 Mbit) Devices           |      |

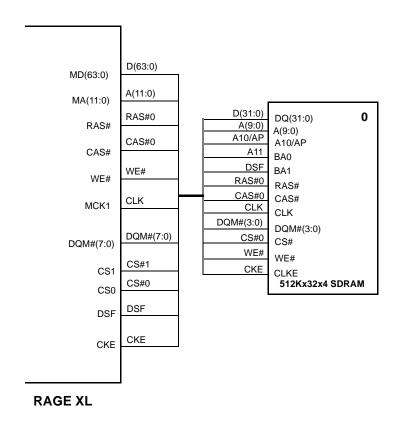

|    | 4.9.7           | SDRAM Interface with 512Kx32x4 (64 Mbit) Devices           |      |

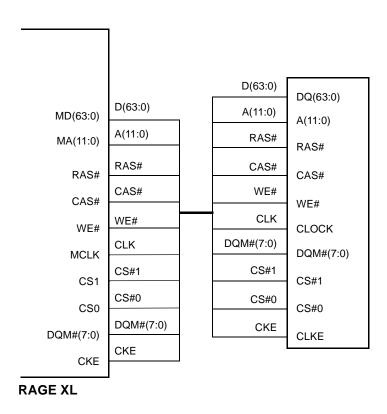

|    | 4.9.8           | SO-DIMM Module Interface                                   |      |

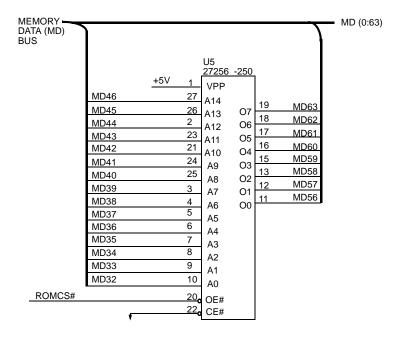

|    | 4.10 EPRO       | OM Interface                                               | 4-21 |

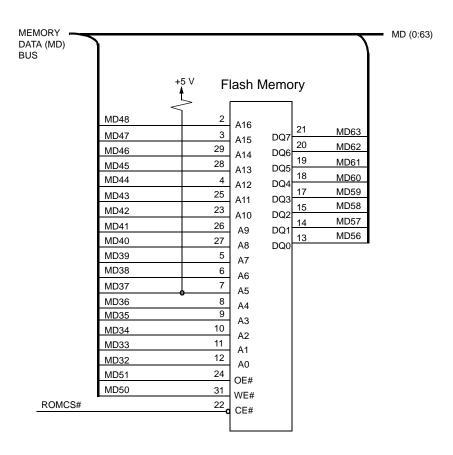

|    | 4.11 Flash      | Memory Interface                                           | 4-22 |

|    | 4.12 Gener      | ral Purpose I/O Control                                    | 4-23 |

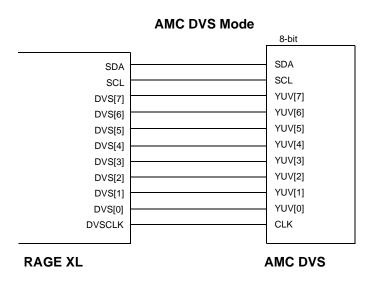

|    | 4.13 ATI N      | Multimedia Channel 2.0 Interface (AMC)                     | 4-23 |

|    |                 | DVS Mode                                                   |      |

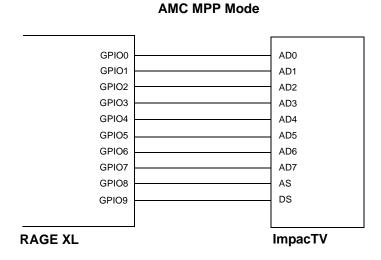

|    | 4.13.2          | MPP Mode                                                   | 4-25 |

|    | 4.14 Analo      | og Output Section                                          | 4-26 |

|    |                 |                                                            |      |

| Ch | apter 5: T      | Timing Specifications                                      |      |

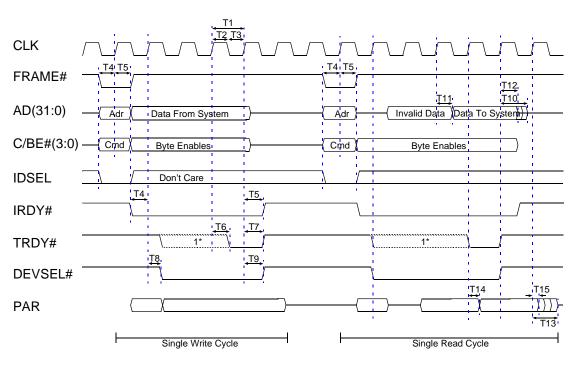

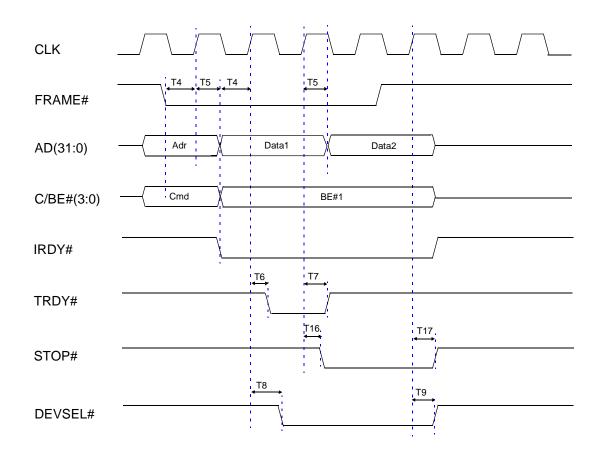

|    | 5.1 Bus Ti      | mings                                                      | 5-1  |

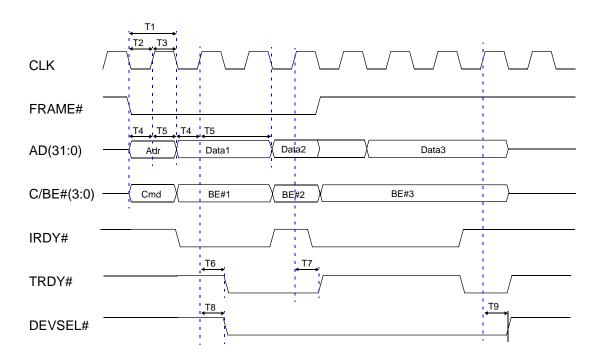

|    | 5.1.1           | Single Read/Write Cycle Timing                             |      |

|    | 5.1.2           | Disconnect On Burst Cycle - PCI Bus.                       | 5-3  |

|    | 5.1.3           | Burst Access Timing - PCI                                  |      |

|    | 5.1.4           | PCI Bus Master Operation                                   | 5-5  |

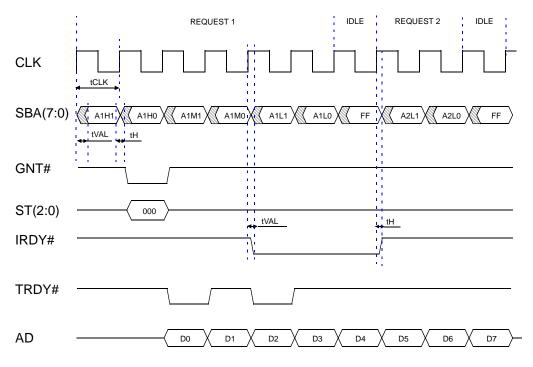

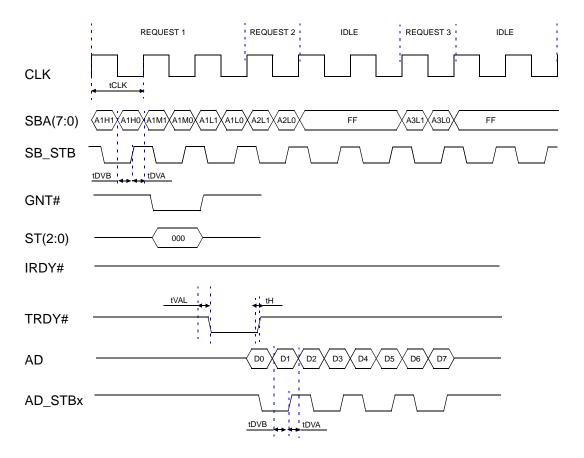

|      | 5.1.5     | AGP Timing                                        |            |

|------|-----------|---------------------------------------------------|------------|

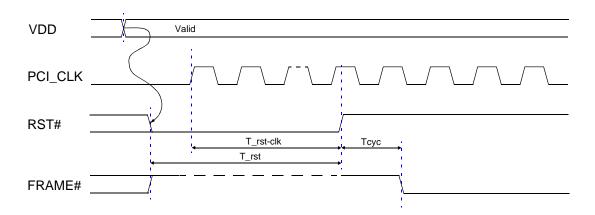

|      | 5.1.6     | Power-up and Reset Timing                         | 5-9        |

| 5.2  | 2 Memo    | ory Timing                                        | 5-10       |

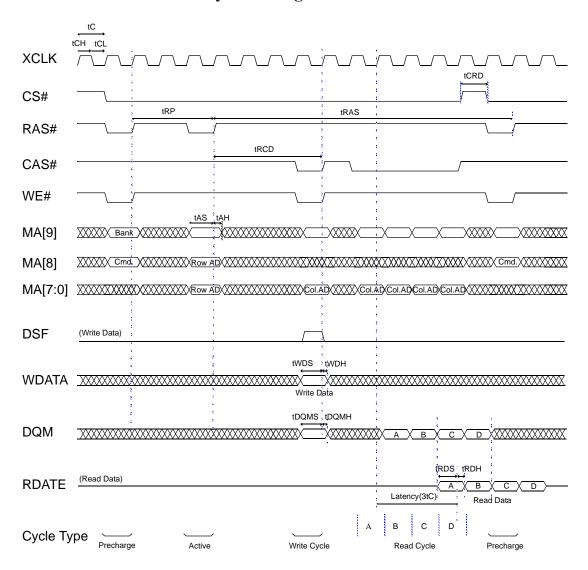

|      | 5.2.1     | SDRAM/SGRAM Cycle Timing                          |            |

|      | 5.2.2     | Memory Controller Register Programming Examples   | 5-13       |

| 5.3  | 3 TMDS    | S Timing                                          | 5-14       |

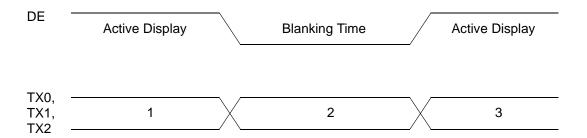

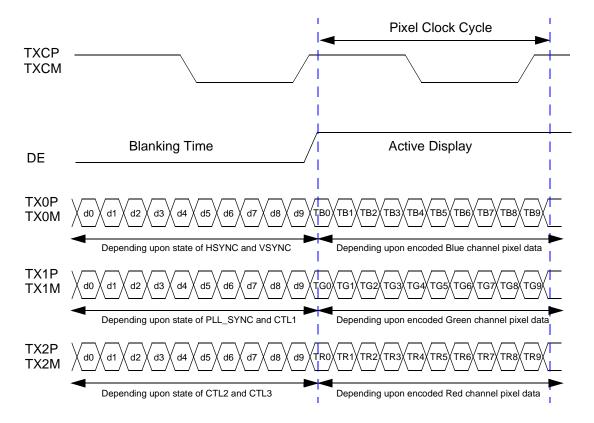

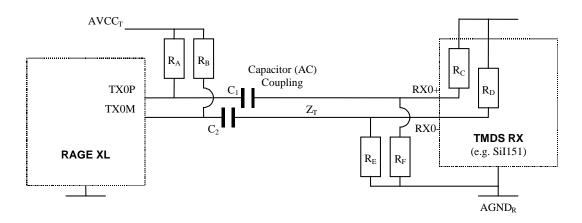

|      | 5.3.1     | TMDS Transmission                                 |            |

|      | 5.3.2     | TMDS Data/Clock Mapping                           | 5-15       |

| Chap | ter 6: I  | Electrical and Physical Data                      |            |

| 6.1  | l Electri | ical Characteristics                              | 6-1        |

|      | 6.1.1     | Maximum Rating Conditions                         |            |

|      | 6.1.2     | Recommended DC Operating Conditions               |            |

|      | 6.1.3     | AC Characteristics                                |            |

|      | 6.1.4     | DC Characteristics                                | 6-4        |

|      | 6.1.5     | Input/Output Specifications                       | 6-6        |

|      | 6.1.6     | DAC Characteristics                               |            |

|      | 6.1.7     | Calculating RSET Resistance (DAC Interface)       |            |

|      | 6.1.8     | Analog Output Specification                       | 6-11       |

| 6.2  | 2 Therm   | nal Characteristics                               | 6-12       |

|      | 6.2.1     | Maximum Ambient Temperature                       | 6-12       |

|      | 6.2.2     | Maximum Recommended Junction and Case Temperature |            |

|      | 6.2.3     | Board Power and Case Temperature Measurements.    | 6-13       |

| 6.3  | B Physic  | cal Dimensions                                    | 6-14       |

| 6.4  | 4 Enviro  | onmental Requirements                             | 6-15       |

|      | 6.4.1     | Storage Temperature                               |            |

|      | 6.4.2     | Relative Humidity                                 |            |

| Chan | ton 7.    | Dianlay Modos                                     |            |

| -    |           | Display Modes                                     |            |

| 7.1  | 1 2D M    | odes                                              | 7-1        |

| 7.2  | 2 Full S  | creen 3D Modes.                                   | <i>7-3</i> |

| 7.3  | B DVD/    | Video Modes                                       | 7-4        |

|      | 7.3.1     | Software MPEG Decoding                            |            |

|      | 7.3.2     | Hardware MPEG Decoding                            |            |

|      |           | -                                                 |            |

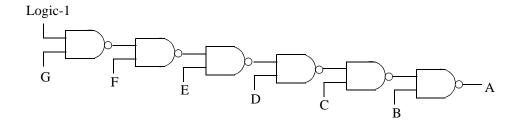

| Chapter 8: NAND Tree Implementation                   |     |

|-------------------------------------------------------|-----|

| 8.1 Overview                                          | 8-2 |

| 8.2 NAND tree in RAGE XL                              | 8-3 |

| 8.3 Test Modes                                        |     |

| 8.3.1 Board Test Modes                                | 8-7 |

| 8.3.2 Other Test Modes                                |     |

| 8.4 Testing Procedure                                 | 8-9 |

| 8.5 Pins Unused in NAND Tree                          | 8-9 |

| Appendix A: Pin Listings  A.1 Pins Sorted by Pin Name |     |

| A.1.1 Pins Sorted by Pin Number                       |     |

| ,                                                     |     |

This page intentionally left blank.

## 1.1 About This Manual

This manual is part of a set of reference documents that provide information necessary to design the RAGE XL graphics controller into a graphics subsystem. These documents are listed on the back of the cover page.

The electrical and thermal characteristics described in this document are specific to the RAGE XL manufactured using TSMC's 0.25µm process, which has voltages of 2.5V core, 3.3V PCI I/O (with 5.0V tolerance), 3.3V AGP, and 3.3V (LVTTL) memory interface. Please contact ATI to obtain information on how to support all of ATI's graphics controllers, steppings, and foundries in one PCB design.

Table 1-1 Summary of this Manual

| Chapter | Description                                                                                            |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | Introduction to this manual.                                                                           |  |  |  |

| 2       | Main features of RAGE XL.                                                                              |  |  |  |

| 3       | Detailed description of the pins, the straps, and pinout differences for various graphics controllers. |  |  |  |

| 4       | Functions of the building blocks of the controller and the interface implementations.                  |  |  |  |

| 5       | Timing diagrams.                                                                                       |  |  |  |

| 6       | Electrical and physical characteristics.                                                               |  |  |  |

| 7       | Display modes supported.                                                                               |  |  |  |

| A       | Pin listing sorted by pin name and by pin number.                                                      |  |  |  |

| В       | Revision History for this manual.                                                                      |  |  |  |

## 1.2 ATI Component Part Number Legend

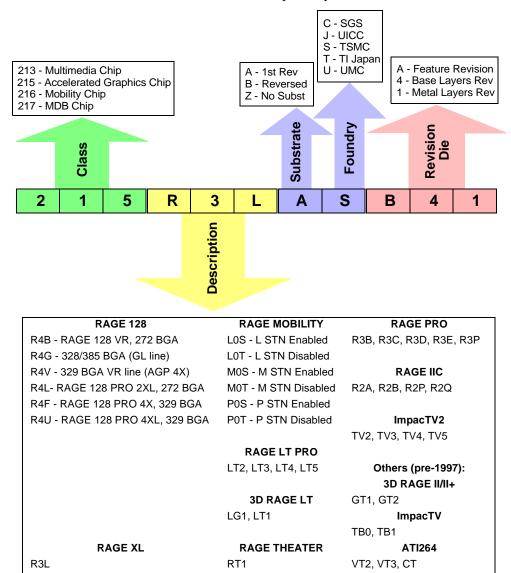

The present manual is intended to cover RAGE XL parts 215R3LASBXX. The manual will be updated periodically to include latest component revisions and respective additional/changed specifications. The figure below shows how to read the coded information contained in a branded ATI component part number.

Figure 1-1. ATI Component Part Number Legend

## 1.3 Conventions and Notations

The following conventions are used for the pins described throughout this manual:

## 1.3.1 Pin/Signal Names

Mnemonics are used throughout this manual to represent pins and external strap resistors. For example, the Device Select pin and the Interrupt Enable external strap are represented by DEVSELb and ENINTb respectively.

All active-low signal names are identified by the suffix 'b' (e.g. BLANKb).

Pins may be identified by their *signal names* or ball references. The terms *pin name* and *signal name* are used indistinguishably in the industry; in this document pin name is used to allow for situations in which pins have different functions, and therfore signal names (e.g. pins in the multimedia group). For such multiplexed pins, the alternate name(s) will be adequately noted.

## 1.3.2 Pin Types

The assigned codes for the various pin types based on operational characteristics are listed in the table below.

Table 1-2 Pin Type Code

| Code | Pin Type / Operational Characteristics |

|------|----------------------------------------|

| I    | Input                                  |

| 0    | Output                                 |

| I/O  | Bi-Directional                         |

| М    | Multifunction                          |

| Pwr  | Power                                  |

| Gnd  | Ground                                 |

| Α    | Analog                                 |

## 1.3.3 Numeric Representation

Hexadecimal numbers are appended with "h" (Intel assembly-style notation) whenever there is a risk of ambiguity. Other numbers are assumed to be in decimal.

When the same pin name (except the following running integer) is used for pins that have identical functions (e.g. AD0, AD1), a short-hand notation is used to refer to all of them (i.e. AD[31:0] refers to AD0, AD1, ..., and AD31).

The above shorthand notation is not to be confused with that used to indicate bit occupation in a register. For example, SUBSYS\_VEN\_ID[15:0] refers to the Product Type Code field that occupies bit positions 0 through 15 within the 16-bit vendor ID register in PCI configuration space.

## 1.3.4 Acronyms

Standard acronyms used in the literature are presumed known and will not be explained. When in doubt, the reader can refer to the following table for a quick check. Less frequently used or ATI-specific acronyms will have the full definition alongside in parenthesis when they appear the first time in the document.

**Table 1-3 Standard Acronyms**

| Acronym          | Full Expression                            |

|------------------|--------------------------------------------|

| ACPI             | Advanced Configuration and Power Interface |

| AGP              | Accelerated Graphics Port                  |

| AMC              | ATI Multimedia Channel                     |

| BGA              | Ball Grid Array                            |

| CRC              | Cyclic Redundancy Check                    |

| DDC              | Display Data Channel                       |

| DFP              | Digital Flat Panel                         |

| DDR              | Double Data Rate                           |

| DPMS             | Display Power Management Signaling         |

| DVS              | Digital Video Stream                       |

| EPROM            | Erasable Programmable Read Only Memory     |

| FIFO             | First In, First Out                        |

| I <sup>2</sup> C | Bus Protocol (Philips Specification)       |

| IDCT             | Inverse Discrete Cosine Transform          |

| LCD              | Liquid Crystal Display                     |

Table 1-3 Standard Acronyms (Continued)

| Acronym | Full Expression                                                                                                          |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LOD     | Level of Details (is referred to texture pixel selection)                                                                |  |  |  |

| MPP     | Multimedia Peripheral Port                                                                                               |  |  |  |

| PEROM   | Flash Programmable and Erasable Read Only Memory                                                                         |  |  |  |

| PQFP    | Plastic Quad Flat Pack                                                                                                   |  |  |  |

| SDR     | Single Data Rate                                                                                                         |  |  |  |

| S/PDIF  | Sony/Phillips Digital Interface                                                                                          |  |  |  |

| TFT     | Thin Film Transister - active matrix                                                                                     |  |  |  |

| TMDS    | Transmission Minimized Differential Signaling                                                                            |  |  |  |

| UV      | Chrominance (also CrCb). Corresponds to the color of a pixel.                                                            |  |  |  |

| VBI     | Vertical Blank Interval                                                                                                  |  |  |  |

| VFC     | VESA Feature Connector                                                                                                   |  |  |  |

| VIP     | Video Interface Port                                                                                                     |  |  |  |

| YUV     | The method of video signal color encoding. Includes luma (Y, black and white component) and chroma (UV, color component) |  |  |  |

This page intentionally left blank.

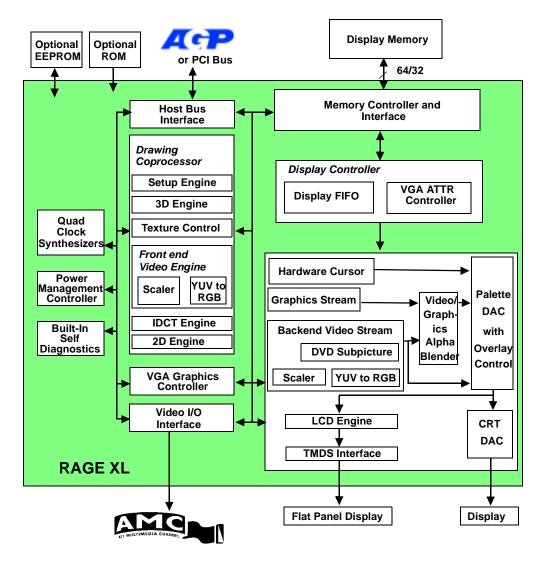

## 2.1 Feature Summary

The RAGE XL graphics controller brings ATI's best of class 2D, 3D, and DVD performance to entry-level PCs and advanced Set-Top boxes. In addition, the RAGE XL is the first graphics controller to offer integrated TMDS transmitter support for Digital Flat Panel (DFP) monitors.

- Outstanding 3D and 2D Performance the RAGE XL delivers superior 3D acceleration and comprehensive 3D support including a 1.2 million triangular/sec set-up engine, single pass trilinear filtering, six perspectively correct texturing modes, video texturing, Gouraud and specular shading, and a host of 3D special effects.

- **Built-in DVD Decoding** ATI RAGE XL's integrated iDCT and Motion Compensation circuitry allow for Hardware DVD playback at full frame rate.

- **Set-Top Box Solution** RAGE XL together with ATI RAGE Theatre (single chip video decoder and encoder) provides excellent set-top graphics and video subsystem. It supports 32-bit true color video/graphics alpha blending.

- Integrated TMDS Flat Panel Support RAGE XL incorporates all the required logic to interface gluelessly with DFP monitors. This provides lowest cost DFP ready implementation through industry standard interfaces, while maintaining support for the existing VGA connector for legacy monitor support. This integrated TMDS transmitter meets VESA Plug-and-Play (P&D) digital transmission standard.

- Full AGP 2X Support RAGE XL incorporates comprehensive support for Intel's AGP including 2x mode with Sideband addressing.

- Full PCI Support RAGE XL supports both PCI 33MHz and PCI 66MHz operation.

## 2.2 General Features

- High integration results in a low cost, small footprint graphics subsystem ideal for motherboard designs.

- AGP version 1.0 support, including 2X mode, Sideband addressing.

- PCI version 2.2 with full bus mastering and scatter / gather support.

- Fully PC 99 compliant.

- Bi-endian support for compliance on a variety of processor platforms.

- Fast response to host commands:

- Deep command FIFO.

- 32-bit wide memory-mapped registers.

- Programmable flat or paged memory model with linear frame buffer access.

- Triple 8-bit palette DAC with gamma correction for true WYSIWYG color. Pixel rates up to 230 MHz.

- Supports flexible memory configurations from 4 MB to 8 MB SDRAM/SGRAM at up to 125 MHz providing bandwidths of up to 1 GByte/sec across a 64-bit interface.

- Memory upgrade via industry standard SGRAM SO-DIMM for reduced board area and higher memory speeds.

- Supports 4MB 1Mx16 or 8MB 2Mx32 SDRAM at up to 125 MHz across a 32-bit interface for lowest cost configurations.

- DDC1 and DDC2B+ for plug and play monitors.

- Power management for full VESA DPMS and EPA Energy Star compliance.

- Integrated hardware diagnostic tests performed automatically upon initialization.

- High quality components through built-in SCAN, Iddq, CRC and chip diagnostics.

- Single chip solution in  $0.25\,\mu$  m, 2.5V CMOS technology, with multiple package options.

- Comprehensive HDKs, SDKs and utilities augmented by full engineering support.

- Complete local language support (contact ATI for current list).

## 2.3 RAGE XL Compatibility with other ATI Chips

For pin compatibility and differences see "Pinout Differences between RAGE XL and other ATI Chips" on page 3-18.

## 2.3.1 Feature Compatibility with RAGE 128 VR

- Supports 64-bit or 32-bit memory bus in 2MB, 4MB, 8MB SDRAM or SGRAM configurations (DDR is not supported).

- Up to 125 MHz SDR 64-bit memory bus.

- Up to 143 MHz SDR 32-bit memory bus.

- Supports hardware-accelerated DVD playback at full frame rates with no additional cost via integrated IDCT and Motion Compensation circuitry.

- Comprehensive support for Accelerated Graphics Port (AGP) including 2X mode, Sideband Addressing and AGP Texturing.

- Superior 3D acceleration and comprehensive 3D support which includes:

- Triangle set-up engine.

- Single-pass tri-linear filtering.

- Six perspectively correct texturing modes.

- Video texturing.

- Gouraud and specular shading.

- A host of 3D special effects video enhancements.

- Floating point setup engine rated at 1.2 million triangles/sec.

- Integrated 230 MHz DAC.

- Increased command FIFO size 512 entries.

- Supports ratiometric expansion.

- Supports RAGE THEATER and ImpacTV2 chips.

## 2.3.2 RAGE 128 Features Not Supported by RAGE XL

- Double-buffered bus-master command tables for MPEG writes through MPP Port.

- Bus-mastered MPP reads.

- MPP enhanced mode. (MPP and TVout will be exactly the same as the RAGE IIC.)

- VIP port.

- Dedicated I<sup>2</sup>C controller pins.

## 2.3.3 Feature Compatibility with the RAGE PRO

RAGE XL has these same features as RAGE PRO:

- 32-bit PCI bus, 3.3V only (5V tol.), with bus mastering support.

- AGP-66 with 1X transfer and AGP-133 with 2X transfer. Both with full sideband addressing only and no support for PIPE#.

- ROM or Flash RAM video BIOS.

- Multimedia.

- Independent I<sup>2</sup>C interface.

- RGB CRT monitor with DDC or AppleSense lines.

- Independent ring and core supplies to enable Iddq testing, NAND tree and internal scan chain.

## 2.4 Features in Detail

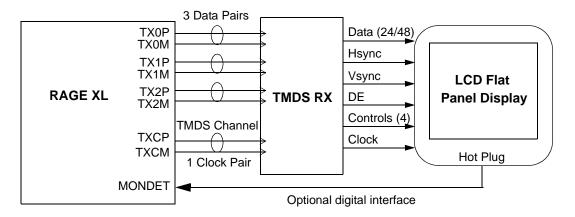

## 2.4.1 Integrated TMDS

- Integrated TMDS transmitter complying to VESA Plug-and-Display (P & D) digital transmission standard.

- TMDS support for both direct-coupling and capacitor-coupling.

## 2.4.2 Digital Flat Panel Support

- Glueless support for industry Digital Flat Panel (20-pin MDR).

- Universal panel interface that supports the followings:

- Color TFT panel up to 1024x780 resolution, up to 24 bit per pixel, single pixel per clock.

- 2/4 levels of frame modulation can be done on 18-bit TFT panels.

- Hardware Z-buffer support with TFT panels.

- Ratiometric Expansion in both VGA Graphics Modes and Accelerated Graphics

Modes. Display modes with resolutions lower than the LCD panel resolution can be

ratiometrically expanded to fill the whole screen. 2- tap horizontal and vertical

filtering to improve both text and graphics image quality. Maximum source resolution

support with vertical filtering:

- Horizontal: 1024 24bpp.

- Vertical: no limit. There is no limit on source resolution if the vertical filtering is disabled.

- Monitor detection through hot plugging support.

- Flat Panel Power Management.

- Standby/Suspend registers for software Power Management support.

- DDC support for LCD monitors. Dedicated I/O pins are available to support DDC on LCD monitor applications.

- Variable Blink Rate Support. Different panels have different response times. Variable blink rate support allows the blinking character/cursor to be seen clearly.

- Backlight Modulation. Pulse Width Modulation (up to 256 levels) for backlight on/off signal to control the brightness of the display.

## 2.4.3 ACPI Power Management

- Advanced Configuration and Power Interface (ACPI) with On, Standby, Suspend and Off modes.

- Register and Timer modes for hardware and software power management.

- Dynamic clock switching.

- Self-refresh SDRAM/SGRAM in Suspend mode.

## 2.4.4 Floating-Point Set-up Engine

This floating-point set-up engine is capable of processing up to 1.2 million triangles per second. By off-loading the set-up function from the CPU, allowing it to focus on 3D geometry and lighting transformations, RAGE XL dramatically improves the performance of the entire 3D pipeline.

Compared with competing first generation set-up engines which only accept fixed-point parameters, requiring the CPU to perform float-to-fixed conversions that can take up to 100 CPU clocks, ATI's floating point architecture opens the door to the highest level of 3D performance.

## 2.4.5 Memory Support

- Single data rate (SDR) SGRAM/SDRAM up to 125 MHz across a 64-bit interface (1.06 GB/s).

- Support only LVTTL.

## 2.4.6 DVD and Video Support

- Hardware DVD decode via integrated motion compensation and IDCT circuitry for full frame rate DVD playback.

- Support for hardware DVD subpicture decoder.

- 4-tap horizontal and 2-tap vertical high quality DVD video scaler, providing smooth images without the jagged edges ("jaggies") common to video products. The scaler provides true color video display, independent of the graphics mode used.

- Front and back end scalers support multi-stream video for video conferencing and other applications.

- YUV direct interface to RAGE THEATER without requiring data to be converted to RGB.

- Enhanced line buffer allows vertical filtering of native MPEG-2 size (720x480) images.

- Special filter circuitry eliminates video artifacts caused by displaying interlaced video on non-interlaced displays.

- Bi-directional bus mastering engine with full YUV planar mode support for superior MPEG-2 and video conferencing.

- Hardware mirroring for flipping video images in video conferencing systems.

- Supports graphics and video keying for effective overlay of video and graphics.

- Smooth video scaling and enhanced YUV to RGB color space conversion for full-screen / full-speed video playback. YUV to RGB color space converter with support for both packed and planar YUV:

- YUV422, YUV410, YUV420.

- RGB32, RGB16/15.

- ATI Multimedia Channel (AMC) video input port, and support for high quality NTSC and PAL TV-out with the ATI ImpacTV2 or RAGE THEATER chips.

- Support 4-bit video and graphics alpha blending ARGB8888 in YUV space for TV out or RGB space for DAC(CRT)/DFP.

#### 2.4.7 2D Acceleration

- Hardware acceleration of Bitblt, Line Draw, Polygon / Rectangle Fill, Bit Masking, Monochrome Expansion, Panning/Scrolling, Scissoring, full ROP support and hardware cursor (up to 64x64x2).

- Game acceleration including support for Microsoft's DirectDraw: Double Buffering, Virtual Sprites, Transparent Blit, Masked Blit and Context Chaining.

- Acceleration in 8/16/24/32 bpp modes.

## 2.4.8 3D Acceleration

- Integrated 1 million triangle/s set-up engine reduces CPU and bus bandwidth requirements and dramatically improves performance of small 3D primitives

- 4K on-chip texture cache dramatically improves large triangle performance.

- Complete 3D primitive support: points, lines, triangles, lists, strips and quadrilaterals and BLTs with Z compare.

- Comprehensive enhanced 3D feature set:

- Full screen or window double buffering for smooth animation.

- Hidden surface removal using 16-bit Z-buffering.

- Z-based fog.

- Fog table integration.

- Edge anti-aliasing.

- Sub-pixel and sub-texel accuracy.

- Gouraud and specular shaded polygons.

- Bi-linear interpolation of texture alpha.

- Modulate alpha function.

- Composite alpha modulate.

- Perspectively correct mip-mapped texturing with chroma-key support.

- Support for single pass bi- and tri-linear texture filtering, vastly improving bi- and tri-linear performance.

- Full support of Direct3D texture lighting.

- Texture compositing.

- Special effects such as complete alpha blending, fog, video textures, texture lighting, reflections, shadows, spotlights, Level of Details (LOD) biasing and texture morphing.

- Dithering support in 16bpp for near 24bpp quality in less memory.

- Texture compression of up to 8:1 using vector quantization.

- Extensive 3D mode support:

- Draw in RGBA32, RGBA16, and RGB16.

- Texture map modes: RGBA32, RGBA16, RGB16, RGB8, ARGB4444, and YUV444.

- Compressed texture modes: YUV422, CLUT4 (CI4), CLUT8 (CI8), and VQ.

## 2.4.9 AMC Support

The 8-bit, bi-directional video port allows direct connection to popular video upgrades such as:

- Video capture / video conferencing.

- Hardware MPEG-2 / DVD player.

- TV Tuner with Intercast support.

- Interface to ATI's ImpacTV or RAGE THEATER chip.

## 2.5 Software Features

- Register-compatible with VGA standards, BIOS-compatible with VESA Super VGA.

- Full-featured, yet simple Windows utilities:

- ATI DeskTop supports panning and scrolling across a virtual workspace;

- Calibration utility for WYSIWYG color.

- Drivers meet Microsoft's rigorous WHQL criteria and are suitable for systems which bear the "Designed for WindowsNT and Windows98" logo.

Table 2-1 Software Support

| Software Support                     | DOS                              | Win 3.x | Win 9x | NT<br>3.51 | NT 4.0 | Win<br>2000 | Mac<br>OS | OS/2 |

|--------------------------------------|----------------------------------|---------|--------|------------|--------|-------------|-----------|------|

| 2D Software Support <sup>1</sup>     | 2D Software Support <sup>1</sup> |         |        |            |        |             |           |      |

| Accelerated driver support           | VESA <sup>2</sup>                | •       | •      | •          | •      | •           | ●7        | •    |

| AutoCAD/ MicroStation                | •                                |         |        |            |        |             |           |      |

| Video Software Support               |                                  |         |        |            |        |             |           |      |

| Microsoft DirectDraw                 |                                  |         | •      |            | •      | •           |           |      |

| Microsoft ActiveMovie/<br>DirectShow |                                  |         | •      |            |        | •           |           |      |

| MPEG-1 software playback             |                                  |         | •      |            | •      | •           |           |      |

| DVD/MPEG-2 software playback         |                                  |         | •      |            |        | •           |           |      |

| QuickTime acceleration               |                                  |         |        |            |        |             | •         |      |

| 3D Software Support                  | 3D Software Support              |         |        |            |        |             |           |      |

| Microsoft Direct3D                   |                                  |         | •      |            |        | •           |           |      |

| QuickDraw 3D RAVE                    |                                  |         |        |            |        |             | •         |      |

| OpenGL                               |                                  |         | ●3     |            | ●3     | ●6          |           |      |

| ATI 3D CIF <sup>4</sup>              | •                                |         | _      |            |        |             |           |      |

| AGP                                  |                                  |         | •      |            | ●5     | •           |           |      |

#### Notes:

- 1 Additional drivers availability from 3rd parties (including SCO and UNIXWARE).

- 2 Direct BIOS support.

- 3 OpenGL ICD.

- 4 ATI's 3D API for the 3D RAGE family.

- 5 NT 4.0 Service Pack 3 supports AGP devices, but does not provide support for AGP Texturing.

- 6 Dependent on NT 5.0 release date.

- 7 Includes QuickDraw support.

# Chapter 3 Pinout and Strap Descriptions

This chapter describes pin and strap assignments for RAGE XL. It also includes a section on pin compatibility between RAGE XL and other ATI controller chips.

## 3.1 Pinout Summary

Table 3-1 Pin Summary by Functional Group

| Functional Group      | RAGE XL<br>BGA-Type Package |  |  |  |

|-----------------------|-----------------------------|--|--|--|

| Clamps                | 2                           |  |  |  |

| Core Ground (VSSC)    | 4                           |  |  |  |

| Core Power (VDDC)     | 5                           |  |  |  |

| CRT Monitor Interface | 9                           |  |  |  |

| Crystal and PLL       | 4                           |  |  |  |

| Host Bus Interface    | 62                          |  |  |  |

| I/O Ground (VSSR)     | 16                          |  |  |  |

| I/O Power (VDDR)+VREF | 9                           |  |  |  |

| Memory Interface      | 93                          |  |  |  |

| Monitor Panel Control | 7                           |  |  |  |

| Multimedia Interface  | 23                          |  |  |  |

| No Connection         | 15                          |  |  |  |

| PCI/AGP Ground (VSSP) | 3                           |  |  |  |

| PCI/AGP Power (VDDP)  | 4                           |  |  |  |

| Test                  | 1                           |  |  |  |

| TMDS Interface        | 15                          |  |  |  |

| Pin Count:            | 272                         |  |  |  |

## 3.2 RAGE XL Pin Assignment: Top View

|    | ٧      | В         | ပ                    | Q         | E         | щ         | g              | I      | 7        | ×                   | 7     | N          | >    | ۵              | œ                     | 7              | מ                   | >      | ž           | >       |    |

|----|--------|-----------|----------------------|-----------|-----------|-----------|----------------|--------|----------|---------------------|-------|------------|------|----------------|-----------------------|----------------|---------------------|--------|-------------|---------|----|

| 20 | MD31   | MD30      | MD29                 | MD26      | MD22      | MD18      | MD14           | MD10   | MD7      | MD4                 | CAS#  | N/C        | HCLK | RAS#           | JQM2                  | JQM5           | MA11                | MA8    | MAS         | MA2     | 20 |

| 19 | MD33   | MD32      | MD28                 | MD25      |           | MD17      | MD13           | 6QW    | MD6      | MD3                 | MD1   | N/C        | N/C  | OMOC           | ЭФМЗ                  | OQM6           | MA10                | MA7    | MA4         | MA1     | 19 |

| 18 | MD35   | MD34 MD32 | MD27                 | MD24 MD25 | MD20 MD21 | MD16 MD17 | MD12 MD13 MD14 | MD8    | MD5      | MD2                 | MD0   | DFP<br>CLK | CKE  | DQM1 DQM0 RAS# | <b>DQM4 DQM3 DQM2</b> | DQM7 DQM6 DQM5 | MA9                 | MA6    | MA3         | MA0     | 18 |

| 11 | MD38   | MD37      | MD36                 | MD23      | MD19      | MD15      | MD11           | VDDR   | NSS      | VDDR                | VDDC  | VDDR       | VREF | DSF            | WE#                   | NSS            | N/C                 | DFPDAT | CS0         | CS1     | 17 |

| 16 | MD41   | MD40      | MD39                 | VDDR      |           |           |                |        |          |                     |       | •          |      |                |                       |                | PCI33EN             | AD0    | AD1         | AD3     | 16 |

| 15 | MD44   | MD43      | MD42                 | NSS       |           |           |                |        |          |                     |       |            |      |                |                       |                | VDDP TESTEN PCI33EN | AD2    | AD4         | AD5     | 15 |

| 41 | MD48   | MD47      | MD46                 | MD45      |           |           |                |        |          |                     |       |            |      |                |                       |                | VDDP.               | AD6    | AD7         | AD8     | 14 |

| 13 | MD52   | MD51      | MD50                 | MD49      |           |           |                |        |          |                     |       |            |      |                |                       |                | N/C                 | CBE0#  | AD_<br>STB0 | AD10    | 13 |

| 12 | MD56   | MD55      | MD54                 | MD53      |           |           |                |        | NSS      | VSS                 | VSS   | VSS        |      |                |                       |                | NSS                 | AD9    | AD11        | AD12    | 12 |

| 11 | MD60   | MD59      | MD58                 | MD57      |           |           |                |        | NSS      | NSS                 | NSS   | NSS        |      |                |                       |                | VDDC                | AD13   | AD15        | AD14    | 11 |

| 10 | WD63   | MD62      | MD61                 | VDDR      |           |           |                |        | NSS      | NSS                 | NSS   | SSA        |      |                |                       |                | PAR                 | \$TOP# | CBE1#       | DEVSEL# | 10 |

| 6  | LPVSS  | LPVDD     | N/C                  | NSS       |           |           |                |        | NSS      | NSS                 | NSS   | NSS        |      |                |                       |                | VDDP                | TRDY#  | FRAME#      | IRDY# [ | 6  |

| 80 | TXVSSR | D/N       | N/C                  | VDDC      |           |           |                |        | <b>!</b> | ı                   | I     | I          | J    |                |                       |                | AGPCLAMP VDDP       | AD16   | AD17 F      | CBE2#   | 8  |

| ۷  | TXCM   | TXCP      | TXVDDR               | VDDR      |           |           |                |        |          |                     |       |            |      |                |                       |                | \SS\                | AD20   | AD18        | AD19    | 7  |

| 9  | MOXT   | TX0P      | TXVDDR TXVSSR TXVDDR | N/C       |           |           |                |        |          |                     |       |            |      |                |                       |                | VDDP                | SBA7   | SBA6        | AD21    | 9  |

| 5  | TX1M   | TX1P      | TXVDDR               | N/C       |           |           |                |        |          |                     |       |            |      |                |                       |                | N/C                 | SBA5   | AD22        | AD23    | 5  |

| 4  | TX2M   | TX2P      | TXVSSR .             | VDDR      | MONDET    | GIOCLAMP  | VDDR           | NSS    | MONID3   | AVSSQ               | AVSSN | PVSS       | AVDD | VDDC           | NSS                   | VDDP           | N/C                 | N/C    | CBE3#       | AD_STB1 | 4  |

| က  | DVS7   | DVS6      | DVS5                 | ROMCS#    | SAD6      | SAD5      | SAD2           | SRDY   | 12CDAT   | MONIDOMONID1 MONID2 | PVDD  | VSY        | SBA1 | SBA3           | N/C                   | ST1            | INTR#               | AD26   | AD24        | AD25    | 3  |

| 7  | DVS4   | DVS3      | DVS2                 | N/C       | SAD7      | SAD3      | SAD1           | DS     | 12CCK    | MONID1              | RSET  | HSY        | SBA0 | SBA2           | ST2                   | #LN5           | RESET#              | AD30   | AD28        | AD27    | 2  |

| 1  | XTALIN | XTAL      | DVS1                 | DVS0      | DVSCLK    | SAD4      | SADO           | BYTCLK | AS       | MONIDOR             | ď     | υ          | В    | SBA4           | SB_STB                | ST0            | REQ# F              | CPUCLK | AD31        | AD29    | 1  |

|    | ٧      | 9         | ပ                    | Q         | E         | щ         | O              | I      | 7        | ×                   | 7     | 2          | >    | ٩              | œ                     | 7              | מ                   | >      | >           | >       | •  |

Figure 3-1 RAGE XL Top View

## 3.3 Host Bus Interface

RAGE XL supports PCI 33MHz, PCI 66MHz, AGP 1X, or AGP 2X buses.

Table 3-2 AGP/PCI Bus Interface

| Signal Name  | I/0 Type                                                                                                     | Description                                                                                                              |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AD[31:0]     | I/O                                                                                                          | System Address                                                                                                           |  |  |  |

| AD_STB[1:0]  | I/O                                                                                                          | Address Strobe (for AGP-133 support)                                                                                     |  |  |  |

| CBE[3:0]#    | I/O                                                                                                          | Bus Command or Byte Enable                                                                                               |  |  |  |

| CPUCLK       | I                                                                                                            | Bus Clock                                                                                                                |  |  |  |

| D[31:0]      | I/O                                                                                                          | Data                                                                                                                     |  |  |  |

| DEVSEL#      | I/O                                                                                                          | Device Select When driven active "low", indicates that the graphics controller has decoded its address. Not used by AGP. |  |  |  |

| FRAME#       | I/O                                                                                                          | Frame Driven by the current bus master to indicate the beginning and duration of an access.                              |  |  |  |

| GNT#         | I                                                                                                            | Grant Signal from Arbiter Indicates to the agent that a bus access has been granted.                                     |  |  |  |

| INTR#        | 0                                                                                                            | Interrupt Request Level triggered. Active "low" by default.                                                              |  |  |  |

| IRDY#        | I/O                                                                                                          | Initiator Ready Indicates that the bus master is able to complete the current data phase of the transaction.             |  |  |  |

| PAR          | 0                                                                                                            | Parity Even parity used (expand on parity detection).                                                                    |  |  |  |

| PCI33EN      | I                                                                                                            | Enable PCI 33MHz Mode                                                                                                    |  |  |  |

| REQ#         | 0                                                                                                            | Request Signal to Arbiter Indicates to the systems' chip set that there is request for bus master cycle.                 |  |  |  |

| RESET#       | I                                                                                                            | PCI Reset                                                                                                                |  |  |  |

| SBA[6:0]     | 0                                                                                                            | Sideband Address Port (for AGP-133 support)                                                                              |  |  |  |

| SBA7 / IDSEL | I/O                                                                                                          | In AGP mode, AGP Sideband Address Port Bit 7  or  In PCI mode, PCI Initialization Device Select                          |  |  |  |

| SB_STB       | 0                                                                                                            | Sideband Strobe (for AGP-133 support)                                                                                    |  |  |  |

| ST[2:0]      | I                                                                                                            | Status Bus (for AGP support)                                                                                             |  |  |  |

| STOP#        | Stop Indicates the current target is requesting the master to stop the current transaction. Not used by AGP. |                                                                                                                          |  |  |  |

Table 3-2 AGP/PCI Bus Interface (Continued)

| Signal Name | I/0 Type | Description                                                                                                  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------|

| TRDY#       | I/O      | Target Ready<br>Indicates the target agent is able to complete the current data<br>phase of the transaction. |

#### NOTE:

In PCI mode, IDSEL will be supported through the SBA7 pin. In AGP mode, IDSEL will be multiplexed through pin AD16 or AD17 depending on the setting of the "IDSEL#' strap. For PCI implementations, leave all unused AGP-only pins as no-connect (i.e. open). Total number of pins in this functional group is 62.

Table 3-3 Host Bus Interface by Bus Type

|                 | Bus Type                  |                           |                           |                            |  |  |  |  |  |

|-----------------|---------------------------|---------------------------|---------------------------|----------------------------|--|--|--|--|--|

| Signal Name     | PCI 33 MHz<br>PCI33EN = 1 | PCI 66 MHz<br>PCI33EN = 0 | AGP 66 MHz<br>PCI33EN = 0 | AGP 133 MHz<br>PCI33EN = 0 |  |  |  |  |  |

| AD[31:0]        | AD[31:0]                  | AD[31:0]                  | AD[31:0]                  | AD[31:0]                   |  |  |  |  |  |

| AD_STB[1:0]     | -                         | -                         | -                         | ADST[1:0]#                 |  |  |  |  |  |

| CBE[3:0]#       | CBE[3:0]#                 | CBE[3:0]#                 | CBE[3:0]#                 | CBE[3:0]#                  |  |  |  |  |  |

| CPUCLK          | CPUCLK                    | CPUCLK                    | CPUCLK                    | CPUCLK                     |  |  |  |  |  |

| DEVSEL#         | DEVSEL#                   | DEVSEL#                   | DEVSEL#                   | DEVSEL#                    |  |  |  |  |  |

| FRAME#          | FRAME#                    | FRAME#                    | FRAME#                    | FRAME#                     |  |  |  |  |  |

| GNT#            | GNT#                      | GNT#                      | GNT#                      | GNT#                       |  |  |  |  |  |

| INTR#           | INTR#                     | INTR#                     | INTR#                     | INTR#                      |  |  |  |  |  |

| IRDY            | IRDY                      | IRDY                      | IRDY                      | IRDY                       |  |  |  |  |  |

| PAR             | PAR                       | PAR                       | PAR                       | PAR                        |  |  |  |  |  |

| REQ#            | REQ#                      | REQ#                      | REQ#                      | REQ#                       |  |  |  |  |  |

| RESET#          | RESET#                    | RESET#                    | RESET#                    | RESET#                     |  |  |  |  |  |

| SBA[6:0]        | -                         | -                         | SBA[6:0]                  | SBA[6:0]                   |  |  |  |  |  |

| SBA7            | IDSEL                     | IDSEL                     | SBA7                      | SBA7                       |  |  |  |  |  |

| SB_STB          | -                         | -                         | -                         | SBST#                      |  |  |  |  |  |

| ST[2:0]         | ST[2:0] -                 |                           | ST[2:0]                   | ST[2:0]                    |  |  |  |  |  |

| STOP#           | STOP#                     | STOP#                     | STOP#                     | STOP#                      |  |  |  |  |  |

| TRDY#           | TRDY#                     | TRDY#                     | TRDY#                     | TRDY#                      |  |  |  |  |  |

| Number of Pins: | 48                        | 48                        | 58                        | 62                         |  |  |  |  |  |

## 3.4 Video Memory Interface

**Table 3-4 Video Memory Interface**

| Signal Name | I/O Type | Description                                                                                                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAS#        | I/O      | Column Address Select                                                                                                                                                                                         |

| CKE         | I/O      | Clock Enable for Memory                                                                                                                                                                                       |

| CS[1:0]     | I/O      | Chip Select for Memory                                                                                                                                                                                        |

| DQM[7:0]    | I/O      | Memory Data Byte Mask                                                                                                                                                                                         |

| DSF         | I/O      | Memory special function enable for all supported SGRAM memory devices with the exception of the SDRAM 512Kx32x4 memory device. (Please refer to <i>Table 4-3</i> for more details on Memory Address Mapping). |

| HCLK        | I/O      | Memory Clock                                                                                                                                                                                                  |

| MA[11:0]    | I/O      | Memory Address Bus                                                                                                                                                                                            |

| MD[31:0]    | I/O      | Memory Data Bus                                                                                                                                                                                               |

| MD[63:32]   | I/O      | Memory Data Bus                                                                                                                                                                                               |

| RAS#        | I/O      | Row Address Select                                                                                                                                                                                            |

| ROMCS#      | I/O      | Chip Select for ROM (video BIOS)                                                                                                                                                                              |

| WE#         | I/O      | Write Enable                                                                                                                                                                                                  |

Note: Total number of pins in this functional group is 93.

## 3.5 BIOS Memory Interface

## 3.5.1 BIOS EPROM Memory Interface Mapping

**Table 3-5 BIOS EPROM Memory Mapping**

| Memory Data Pins    | EPROM           | Interface | Flash EPROM Interface |         |  |  |

|---------------------|-----------------|-----------|-----------------------|---------|--|--|

| Welliory Data Filis | 64KB            | 128KB     | 64KB                  | 128KB   |  |  |

| MD[47:32]           | A[15:0] A[15:0] |           | A[15:0]               | A[15:0] |  |  |

| MD[48]              | -               | A[16]     | -                     | A[16]   |  |  |

| MD[50]              | -               | -         | WE#                   | WE#     |  |  |

| MD[51]              | OE#             | OE#       | OE#                   | OE#     |  |  |

| MD[63:56]           |                 | D[7       | 7:0]                  |         |  |  |

| ROMCS#              | CS#             | CS#       | CS#                   | CS#     |  |  |

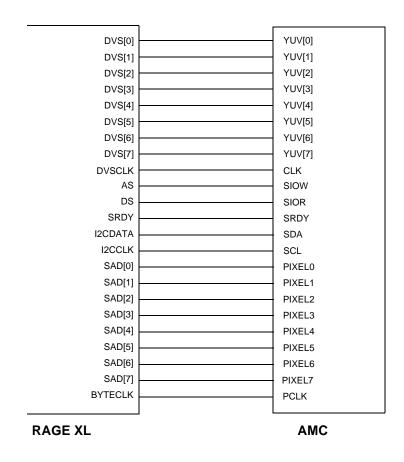

## 3.6 Multimedia Interface

## 3.6.1 Multimedia Interface Pinout

Table 3-6 AMC Pinout

| Signal Name | Pin Type | Description                                                    |

|-------------|----------|----------------------------------------------------------------|

| AS          | I/O      | MPP Address Strobe                                             |

| BYTECLK     | I/O      | BYTECLK (for ImpacTV)                                          |

| DS          | I/O      | MPP Data Strobe                                                |

| DVS[7:0]    | I        | DVS Data In                                                    |

| DVSCLK      | I        | DVS Clock In                                                   |

| I2CCK       | 0        | I <sup>2</sup> C Clock Out                                     |

| I2CDAT      | I/O      | I <sup>2</sup> C Data In/Out                                   |

| SAD[7:0]    | I/O      | Address / data for MPP[7:0] TV out data for ImpacTV interface. |

| SRDY / IRQ  | I/O      | MPP Ready / Interrupt                                          |

Note: Total number of pins in this functional group is 23.

## 3.6.2 Standard Multimedia Configurations

**Table 3-7 Standard Multimedia Configurations**

| Signal Name | MPP port     | ITU-601 Video<br>Capture Port | DVS port | I <sup>2</sup> C     | ImpactTV or<br>Rage Theater | GP Register<br>Bit |

|-------------|--------------|-------------------------------|----------|----------------------|-----------------------------|--------------------|

| DVS(7:0)    |              | I601DAT(7:0)                  | YUV(7:0) |                      |                             |                    |

| DVSCLK      |              | I601CLK                       | CLK      |                      |                             |                    |

| SAD(7:0)    | SAD(7:0)     | *                             | *        | *                    | Pixel Data                  | GPIO(7:0)          |

| AS          | SIOW<br>(DS) | *                             | *        | *                    | *                           | GPIO(8)            |

| DS          | SIOR (AS)    | *                             | *        | *                    | *                           | GPIO(9)            |

| SRDY        | SRDY/IRQ     | *                             | *        | *                    | *                           | GPIO(10)           |

| BYTECLK     | *            | *                             | *        | *                    | Pixel Clock                 | GPIO(11)           |

| I2CDAT      | *            | *                             | *        | I <sup>2</sup> CDATA | *                           | GPIO(12)           |

| I2CCK       | *            | *                             | *        | I <sup>2</sup> CCLK  | *                           | GPIO(13)           |

| MONID(3:0)  | *            | *                             | *        | *                    | *                           | GPIO(17:14)        |

| DFPCLK      | *            | iHREF                         | *        | *                    | *                           |                    |

| DFPDAT      | *            | iVSYNC                        | *        | *                    | *                           |                    |

#### Notes:

- Any extra pins not used (\*) in a particular mode can be used as general purpose I/O pins (GPIO)

- GPIO(17:14) are mapped from LT\_GIO register (offset 0\_2A index 7) please refer to Rage XL Register Specification

- iHREF and iVSYNC are used as inputs for ITU video capture, and their directions are controlled by TMDS register TEST\_IO Index 28. **TMDS and ITU-601 features are mutually exclusive in B41 revision**.

## 3.7 TMDS Interface for Digital Flat Panels

Table 3-8 TMDS Interface

| Signal Name | Pin Type | Description                                               |

|-------------|----------|-----------------------------------------------------------|

| LPVDD       | I        | TMDS PLL Power                                            |

| LPVSS       | 0        | TMDS PLL Ground                                           |

| TX0M        | 0        | TX0-<br>TMDS (-) Differential Transmitter Output For Blue |

| TX0P        | 0        | TX0+ TMDS (+) Differential Transmitter Output For Blue    |

Table 3-8 TMDS Interface (Continued)

| Signal Name | Pin Type | Description                                                |

|-------------|----------|------------------------------------------------------------|

| TX1M        | 0        | TX1-<br>TMDS (-) Differential Transmitter Output For Green |

| TX1P        | 0        | TX1+ TMDS (+) Differential Transmitter Output For Green    |

| TX2M        | 0        | TX2-<br>TMDS (-) Differential Transmitter Output For Red   |

| TX2P        | 0        | TX2+ TMDS (+) Differential Transmitter Output For Red      |

| TXCM        | 0        | TXC-<br>TMDS (-) Differential Transmitter Output Clock     |

| TXCP        | 0        | TXC+ TMDS (+) Differential Transmitter Output Clock        |

| TXVDDR (X2) | I        | TMDS Transmitter Power                                     |

| TXVSSR (X3) | 0        | TMDS Transmitter Ground                                    |

Note: Total number of pins in this functional group is 15.

The TMDS transmitter encodes the 8-bit LPIXD data into the 10-bit PIXD10B encoded word. Special sync characters are used to delimit valid pixel data as shown below in TMDS out-of-band patterns table. For more details, refer to the VESA Plug-and-Display standard specifications.

Table 3-9 TMDS Sync Character Table

| HSYNC<br>PLL_SYNC<br>CTL2 | VSYNC<br>PLL_SYNC<br>CTL3 | d0 | d1 | d2 | d3 | d4 | d5 | d6 | d7 | d8 | d9 |

|---------------------------|---------------------------|----|----|----|----|----|----|----|----|----|----|

| 0                         | 0                         | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  |

| 1                         | 0                         | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  |

| 0                         | 1                         | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| 1                         | 1                         | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

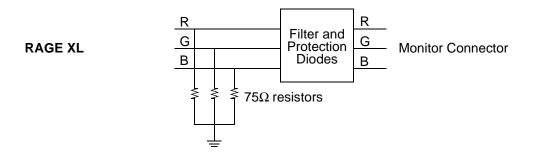

## 3.8 CRT Monitor Interface

## 3.8.1 CRT Monitor Interface

**Table 3-10 CRT Monitor Interface**

| Signal Name | Pin Type | Description                                  |

|-------------|----------|----------------------------------------------|

| AVDD        | A-I      | DAC VDD (2.5V)                               |

| AVSSQ       | A-O      | DAC VSS<br>Quite ground used for bandgap.    |

| AVSSN       | A-O      | DAC VSS noisy ground used as a current dump. |

| В           | A-O      | Blue Signal for Monitor                      |

| G           | A-O      | Green Signal for Monitor                     |

| HSYNC       | 0        | Horizontal Sync Output                       |

| R           | A-O      | Red Signal for Monitor                       |

| RSET        | A-O      | Internal Reference                           |

| VSYNC       | 0        | Vertical Sync Output                         |

Note: Total number of pins in this functional group is 9.

## 3.8.2 Panel Control Interface

**Table 3-11 Panel Control Interface**

| Signal Name | Pin Type | Description                           |

|-------------|----------|---------------------------------------|

| DFPCLK      | I/O      | Flat Panel Clock                      |

| DFPDAT      | I/O      | Flat Panel Data                       |

| MONDET      | I        | Hot Plug Monitor Detect               |

| MONID[0]    | I/O      | Flat Panel DIGON                      |

| MONID[2:1]  | I/O      | DDC Monitor Sensing                   |

| MONID[3]    | I/O      | Apple Monitor Sensing/Flat Panel BLON |

Note: Total number of pins in this functional group is 7.

## 3.9 Miscellaneous Pins

## 3.9.1 Internal PLL and External Crystal Interface

**Table 3-12 External Crystal Interface Pins**

| Signal Name | Pin Type | Description                             |

|-------------|----------|-----------------------------------------|

| PVDD        | A-I      | Phase Lock Loop Power (2.5 V)           |

| PVSS        | A-O      | Phase Lock Loop Ground                  |

| XTALIN      | I        | PLL Reference Clock -OR- MXCLK Source 4 |

| XTALOUT     | 0        | PLL Reference Clock                     |

Note: Total number of pins in this functional group is 4.

## 3.9.2 Testing Pin

**Table 3-13 Testing Pin**

| Pin Name | Pin Type | Description               |  |

|----------|----------|---------------------------|--|

| TESTEN   | Ι        | Test Enable for test mode |  |

Note: Total number of pins in this functional group is 1.

## 3.9.3 Clamping Pins

Table 3-14 Clamping Pins

| Pin Name              | Pin Type | Description                                                  |

|-----------------------|----------|--------------------------------------------------------------|

| AGPCLAMP <sup>a</sup> | 1        | Clamp for 5V Tolerance / Signal integrity on PCI             |

| GIOCLAMP <sup>b</sup> | 1        | Clamp for 5V Tolerance / Signal integrity on Memory and GIOs |

#### Notes:

a) AGPCLAMP pin should be connected to 3.3V power supply in AGP system and PCI system with 3.3V signalling. In a PCI system with 5.0V signaling, this pin should be connected to 5.0V.

b) If the GIO signal is 3.3V, GIOCLAMP pin should be connected to 3.3V power supply. If the GIO signal is 5.0V, this pin should be connected to 5.0V power supply.

## 3.9.4 Power and Ground Pins

Table 3-15 TMDS Power Pins

| Signal Name | Pin Type | Description             |

|-------------|----------|-------------------------|

| LPVDD       | I        | TMDS PLL Power          |

| LPVSS       | 0        | TMDS PLL Ground         |

| TXVDDR (X2) | I        | TMDS Transmitter Power  |

| TXVSSR (X3) | 0        | TMDS Transmitter Ground |

**Table 3-16 Power and Ground Pins**

| Signal Name | Pin Type | Description                                       |

|-------------|----------|---------------------------------------------------|

| AVDD        | I        | Analog DAC Power - 2.5V                           |

| AVSSN       | 0        | Analog DAC Ground                                 |

| AVSSQ       | 0        | Analog DAC Ground                                 |

| PVDD        | I        | PLL Power - 2.5V                                  |

| PVSS        | 0        | PLL Ground                                        |

| VDDC        | I        | Core Power - 2.5V For the graphics controller.    |

| VDDP        | I        | PCI/AGP Power - 3.3V<br>For PCI or AGP interface. |

| VDDR        | I        | I/O Power - 3.3V<br>For memory and multimedia.    |

| VSS         | 0        | Ground                                            |

**Table 3-17 Power and Ground Pins Count**

| Signal Name | Number of Pins |

|-------------|----------------|

| VDDC        | 4              |

| VDDP        | 4              |

| VDDR        | 9 (8+VREF)     |

| VSS         | 48             |

| AVSSQ       | 1              |

| AVSSN       | 1              |

| AVDD        | 1              |

| LPVDD       | 1              |

| LPVSS       | 1              |

**Table 3-17 Power and Ground Pins Count (Continued)**

| Signal Name | Number of Pins |

|-------------|----------------|

| TXVDDR      | 2              |

| TXVSSR      | 3              |

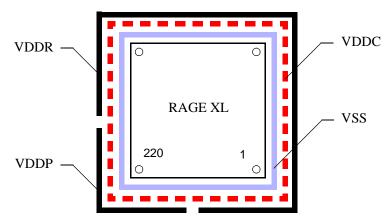

## Power and Ground Rings for the RAGE XL

### **Top View**

$VDDC = 2.5V \pm 5\%$

$VDDP = 3.3V \pm 10\%$

$VDDR = 3.3V \pm 10\%$

Figure 3-2 Power and Ground Rings

# 3.10 Strapping Options

RAGE XL uses two groups of straps:

- External Straps

These straps are located on the Memory Address pins and are required for proper initialization of the chip before bus cycles can occur.

- BIOS ROM Straps

These straps are stored in BIOS ROM.

#### **Note 1: Clarification of the first bullet:**

Although RAGE XL contains internal pull-up and pull-down resistors, external pull-up/pull-down resistor straps are required to ensure proper initialization of the ASIC for all implementations.

## 3.10.1 Standard Boot-up Sequence

The boot-up sequence is as follows:

- 1. PCI reset is asserted.

- 2. External straps are fed into the chip.

- 3. PCI reset is deasserted.

- 4. External straps are flopped in.

- 5. ROM state machine begins to read "ROM based straps".

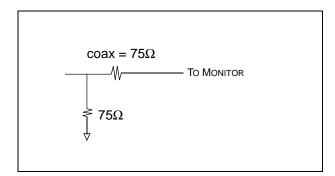

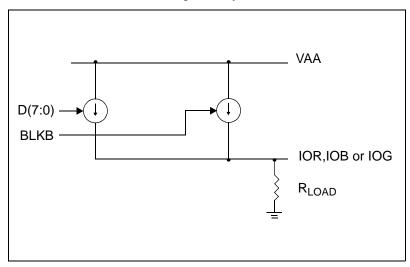

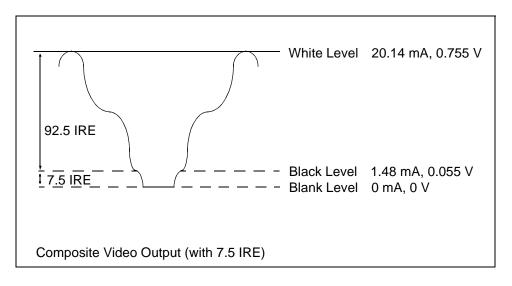

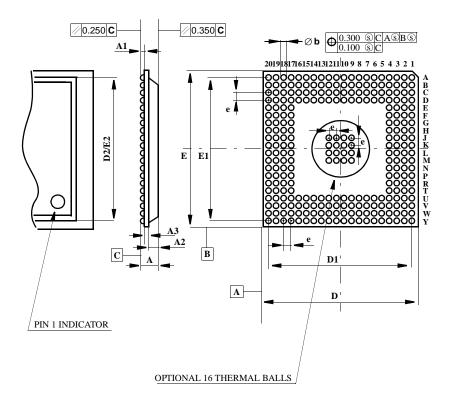

- 6. PCI may begin its first transfer taken but not serviced yet.